In this Verilog project, Verilog code for Full Adder is presented. Both behavioral and structural Verilog code for Full Adder is implemented.

Verilog code for the full adder using behavioral code:

// fpga4student.com // FPGA projects, VHDL projects, Verilog projects // Verilog code for full adder // Behavioral code for full adder module Full_Adder_Behavioral_Verilog( input X1, X2, Cin, output S, Cout ); reg[1:0] temp; always @(*) begin temp = {1'b0,X1} + {1'b0,X2}+{1'b0,Cin}; end assign S = temp[0]; assign Cout = temp[1]; endmodule // fpga4student.com // FPGA projects, VHDL projects, Verilog projects // Verilog code for full adder // Testbench code of the behavioral code for full adder `timescale 10ns/ 10ps; module Testbench_Behavioral_adder(); reg A,B,Cin; wire S,Cout; //Verilog code for the structural full adder Full_Adder_Behavioral_Verilog Behavioral_adder( .X1(A), .X2(B), .Cin(Cin), .S(S), .Cout(Cout) ); initial begin A = 0; B = 0; Cin = 0; #5; A = 0; B = 0; Cin = 1; #5; A = 0; B = 1; Cin = 0; #5; A = 0; B = 1; Cin = 1; #5; A = 1; B = 0; Cin = 0; #5; A = 1; B = 0; Cin = 1; #5; A = 1; B = 1; Cin = 0; #5; A = 1; B = 1; Cin = 1; #5; end endmodule

Simulation wave of the behavioral Verilog code for the full adder:

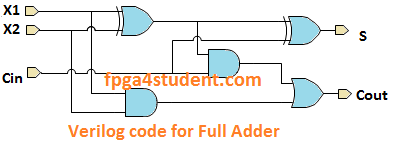

Verilog code for the full adder using structural code:

// fpga4student.com // FPGA projects, VHDL projects, Verilog projects // Verilog code for full adder // Structural code for full adder module Full_Adder_Structural_Verilog( input X1, X2, Cin, output S, Cout ); wire a1, a2, a3; xor u1(a1,X1,X2); and u2(a2,X1,X2); and u3(a3,a1,Cin); or u4(Cout,a2,a3); xor u5(S,a1,Cin); endmodule // fpga4student.com // FPGA projects, VHDL projects, Verilog projects // Verilog code for full adder // Testbench code of the structural code for full adder `timescale 10ns/ 10ps; module Testbench_structural_adder(); reg A,B,Cin; wire S,Cout; //Verilog code for the structural full adder Full_Adder_Structural_Verilog structural_adder( .X1(A), .X2(B), .Cin(Cin), .S(S), .Cout(Cout) ); initial begin A = 0; B = 0; Cin = 0; #10; A = 0; B = 0; Cin = 1; #10; A = 0; B = 1; Cin = 0; #10; A = 0; B = 1; Cin = 1; #10; A = 1; B = 0; Cin = 0; #10; A = 1; B = 0; Cin = 1; #10; A = 1; B = 1; Cin = 0; #10; A = 1; B = 1; Cin = 1; #10; end endmodule

Simulation wave of the structural Verilog code for the full adder:

Recommended Verilog projects:

2. Verilog code for FIFO memory

3. Verilog code for 16-bit single-cycle MIPS processor

4. Programmable Digital Delay Timer in Verilog HDL

5. Verilog code for basic logic components in digital circuits

6. Verilog code for 32-bit Unsigned Divider

7. Verilog code for Fixed-Point Matrix Multiplication

8. Plate License Recognition in Verilog HDL

9. Verilog code for Carry-Look-Ahead Multiplier

10. Verilog code for a Microcontroller

11. Verilog code for 4x4 Multiplier

12. Verilog code for Car Parking System

13. Image processing on FPGA using Verilog HDL

14. How to load a text file into FPGA using Verilog HDL

15. Verilog code for Traffic Light Controller

16. Verilog code for Alarm Clock on FPGA

17. Verilog code for comparator design

18. Verilog code for D Flip Flop

19. Verilog code for Full Adder

20. Verilog code for counter with testbench

21. Verilog code for 16-bit RISC Processor

22. Verilog code for button debouncing on FPGA

23. How to write Verilog Testbench for bidirectional/ inout ports

3. Verilog code for 16-bit single-cycle MIPS processor

4. Programmable Digital Delay Timer in Verilog HDL

5. Verilog code for basic logic components in digital circuits

6. Verilog code for 32-bit Unsigned Divider

7. Verilog code for Fixed-Point Matrix Multiplication

8. Plate License Recognition in Verilog HDL

9. Verilog code for Carry-Look-Ahead Multiplier

10. Verilog code for a Microcontroller

11. Verilog code for 4x4 Multiplier

12. Verilog code for Car Parking System

13. Image processing on FPGA using Verilog HDL

14. How to load a text file into FPGA using Verilog HDL

15. Verilog code for Traffic Light Controller

16. Verilog code for Alarm Clock on FPGA

17. Verilog code for comparator design

18. Verilog code for D Flip Flop

19. Verilog code for Full Adder

20. Verilog code for counter with testbench

21. Verilog code for 16-bit RISC Processor

22. Verilog code for button debouncing on FPGA

23. How to write Verilog Testbench for bidirectional/ inout ports

24. Tic Tac Toe Game in Verilog and LogiSim

25. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-1)

26. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-2)

27. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-3)

28. Verilog code for Decoder25. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-1)

26. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-2)

27. 32-bit 5-stage Pipelined MIPS Processor in Verilog (Part-3)

29. Verilog code for Multiplexers

30. N-bit Adder Design in Verilog

31. Verilog vs VHDL: Explain by Examples

32. Verilog code for Clock divider on FPGA

33. How to generate a clock enable signal in Verilog

34. Verilog code for PWM Generator

35. Verilog coding vs Software Programming

No comments:

Post a Comment