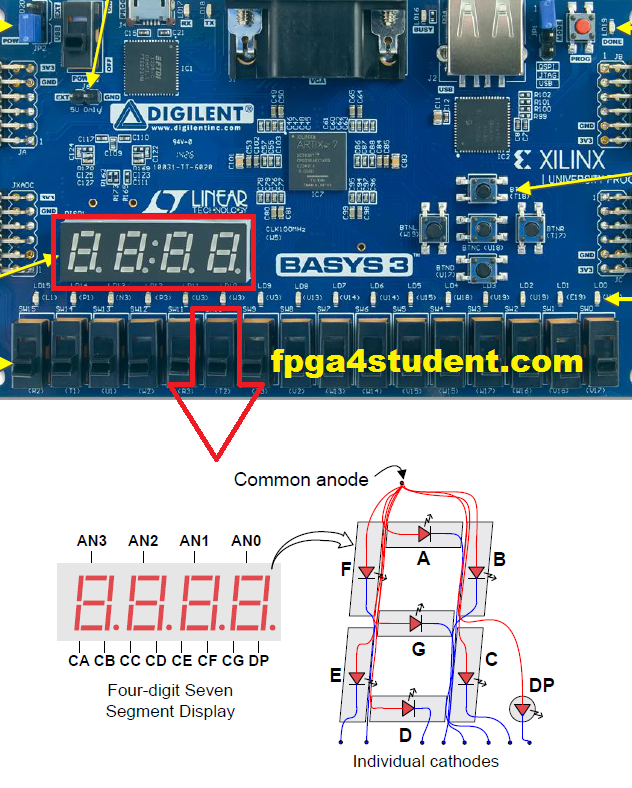

Last time, I wrote a full FPGA tutorial on how to control the 4-digit 7-segment display on Basys 3 FPGA. A full Verilog code for displaying a counting 4-digit decimal number on the 7-segment display was also provided.

This VHDL project will present a full VHDL code for seven-segment display on Basys 3 FPGA. The seven-segment display on Basys 3 FPGA will be used to display a 4-digit hexadecimal number which is counting up every 1 second.