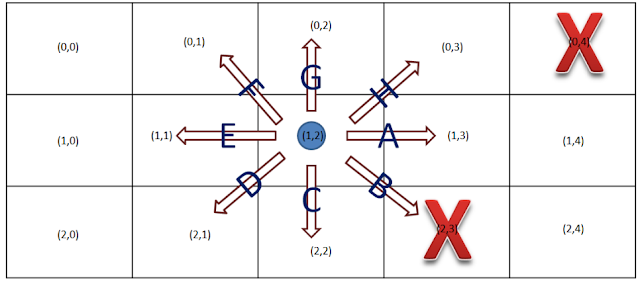

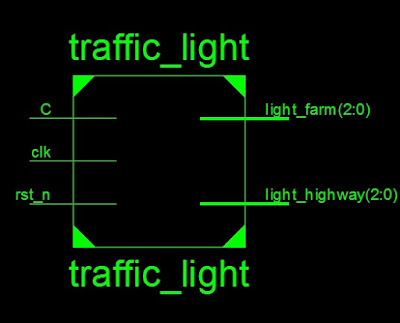

In this project, a MIPS Assembly program is written to move a virtual point robot on a given environment.

The dimensions of the environment, starting coordinates of the robot, locations of obstacles and moving commands will be provided. The program should move the robot according to the given provided commands, environment dimensions, and obstacle coordinates. At the end of the program, the final coordinate of the robot should be presented.

Below is an example of the input :

3x5#(1,2)#(0,4),(2,3)#ACCAGGGACEEEFFDB#

3x5 is the dimension of the provided environment.

(1,2) is the initial coordinate of the robot.

(0,4) and (2,3) are the coordinates of the obstacles.

# is the character which separates the input parts.

Virtual presentation of the example environment